The 10 Gigabit MAC/transceiver gives me 64 bit data words. I currently think I am giving and getting 64 bit data words, but I am really only using 32 bits. I came to this conclusion after I tried reading a 64 bit word and saw the data was simply two repeated 32 bit words. Additionally some random person on the internet said that the MicroBlaze data bus is 32-bit and you have to use some sort of data width converter ip.

Out of luck… I don’t know how to use the converter, but I am sure there is a way to properly convert this by using LabVIEW FPGA. So for starters, this means I can remove my AXI4 Stream Data FIFOs and keep the two 32-bit versions. I’ll also throw in support for TKEEP while I am at it.

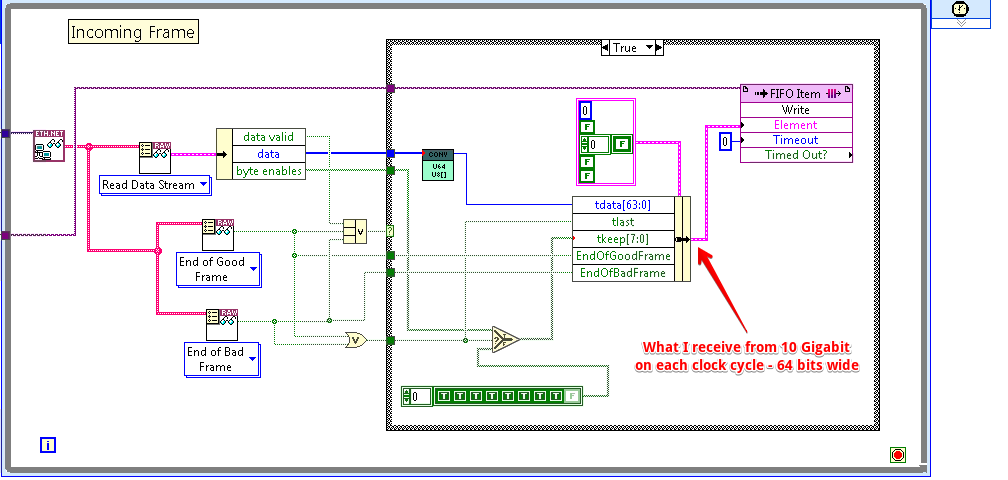

So the “Receive Ethernet Frame” code from the 10 Gigabit transceiver/MAC looks like this:

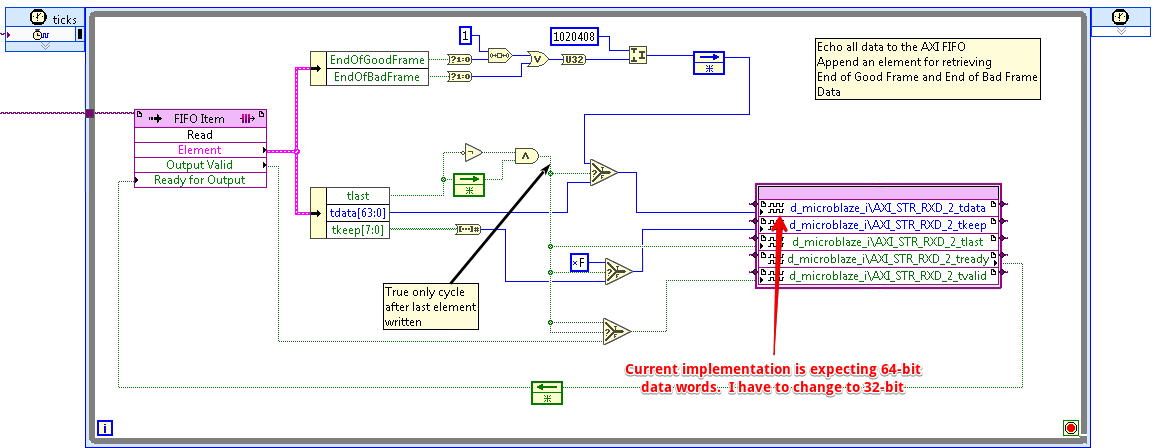

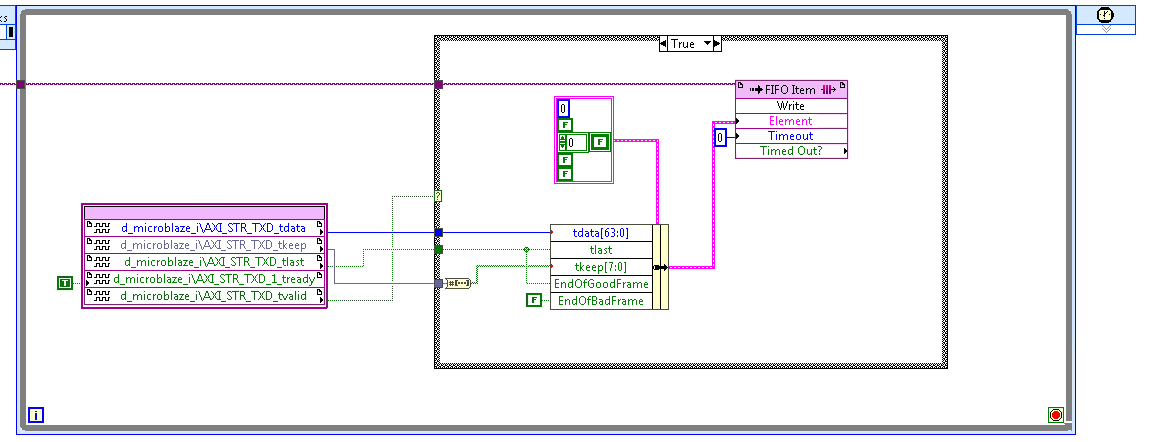

I have to convert this 64-bit data stream in to a 32-bit data stream before I send it in to the MicroBlaze. Here is the current/erroneous implementation:

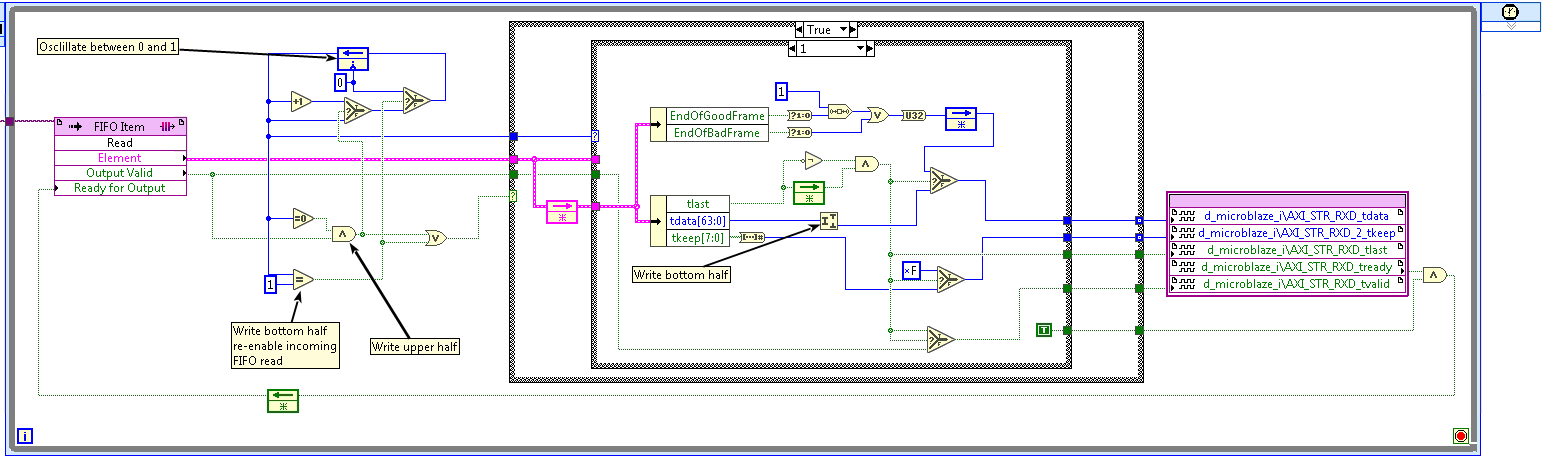

So what do I have to do? I have to read one element from the LabVIEW FIFO – the FIFO on the left, write the upper half of the 32 bit word in one cycle, and not read from the LabVIEW FIFO for the next clock cycle and to write the lower half of the 32 bit word. Want to see the power of LabVIEW? It is 7:22 AM right now… [elevator music/jeopardy music starts playing in the background]

Now it is 8:07 AM and I have finished re-factoring this loop. I am writing the upper half of each 64 bit word in one cycle, and am writing the bottom half during the next clock cycle. I am also keeping the logic that appends an extra word which contains the “EndOfGoodFrame”, and “EndOfBadFrame” boolean values. Since I am writing 32-bit words now, I am only appending one word.

Here is the full loop:

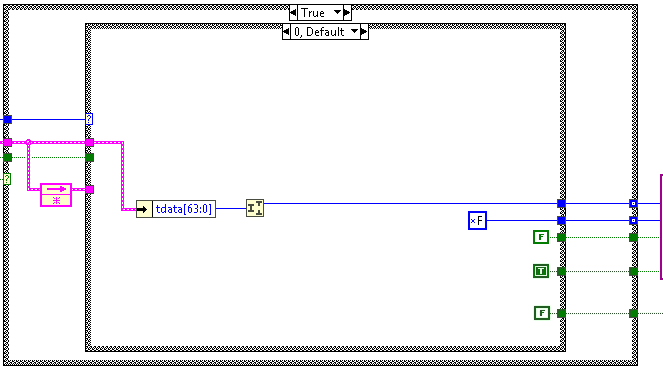

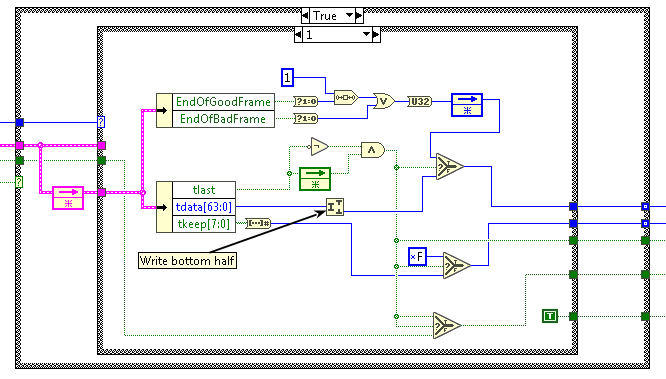

And a close up of Case 0 of the innermost Case Structure:

And a close up of Case 1:

I now have to do this for the other direction – convert a LabVIEW FIFO packet to an AXI 32-bit stream. Here is the current implementation:

The signal on AXI_STR_TXD_data is a U32 and I have to collect 2 of these values and insert them in to the FIFO on the right side. I am going to have to think about this for a bit, but I have to get ready and go to work. So I may not finish this before leaving.

Thanks and have a nice day!

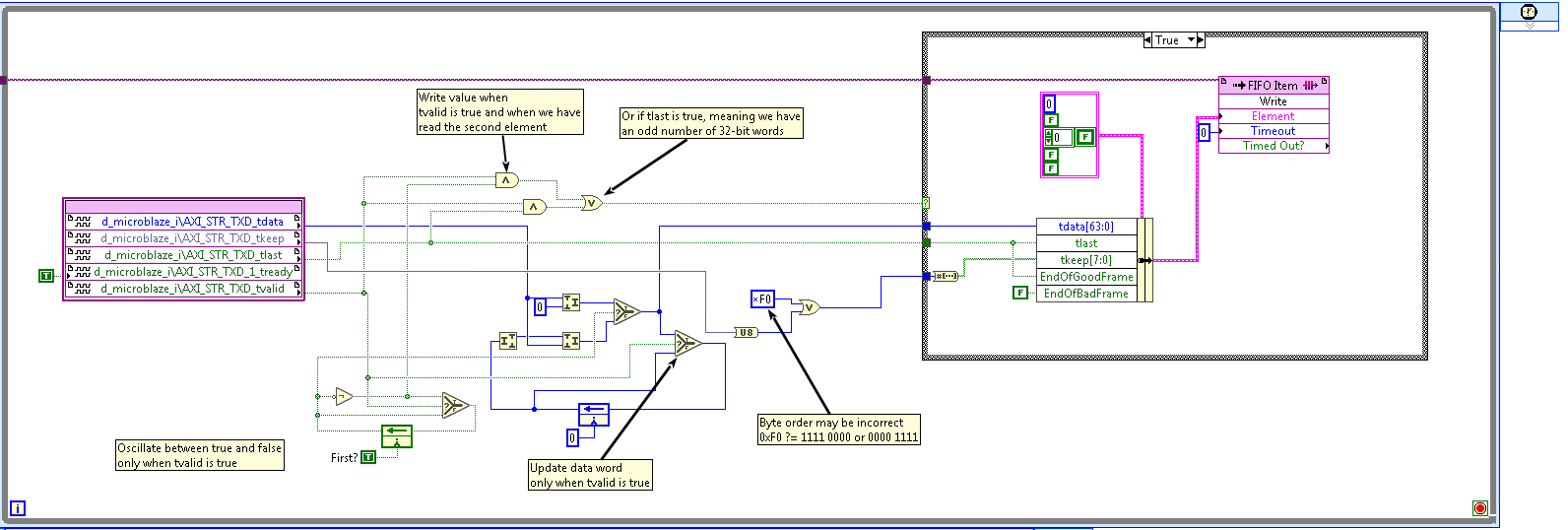

Update: Okay, this is not that pretty, but here is my first-cut “20 minutes” version:

Now I have to go and get ready! But I’ll be sure to set everything to synthesize before I leave…