Filter Market Data Messages in an FPGA – part 3

Note: Skip directly to GitHub.com to download the source code by following this link:

- https://github.com/fpganow/MarketData

- System Requirements:

- LabVIEW 2016

- LabVIEW 2016 FPGA Module

- http://www.ni.com/labview/

This post will cover the next iteration of implementing an OrderBook inside an FPGA that is based on a NASDAQ ITCH 4.1 market data feed.

Some time has passed and I have finally found enough time to finish all the code changes required for the two (2) components listed below, along with the requisite test harnesses to validate.

Starting off, here are the components of an FPGA-based OrderBook

- ITCH Parser

- FPGA loop that listens to incoming data from a Network Interface Card that parses, filters and translates each incoming message and sends the appropriate message/command to the OrderBook loop.

- OrderBook

- FPGA loop that reads and writes Orders to memory using an insertion sort algorithm. The Orderbook is currently able to support only one instrument and one side. It’s capacity is 1,000 elements, which through the power of LabVIEW for FPGA can be easily adjusted, but that is not important right now. The OrderBook currently supports two commands: add order and get all orders. The get all orders command is meant to be used by a user or client application for trading and other purposes.

Using Test Driven Development, Here Are the Test Harnesses

- ITCH Parser Test Harness

- Input: A file containing raw ITCH 4.1 market data messages (generated using createItch.py)

- Output: Array of OrderBook operations

- OrderBook Test Harness

- Input: An array of OrderBook operations

- Output: A sorted array of Orders

What Does a Test Harness Look Like?

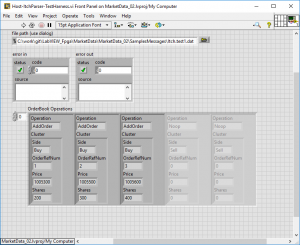

Here is a screenshot of the Front Panel diagram for the ITCH Parser Test Harness:

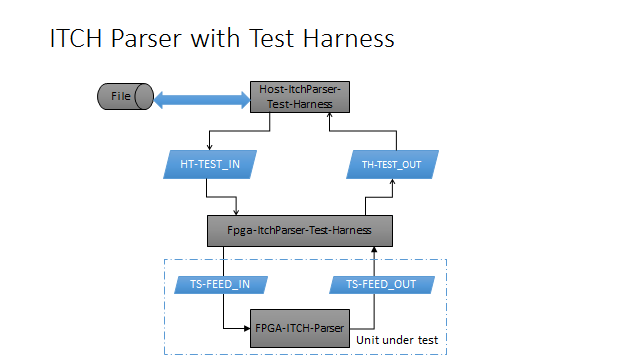

and here is a flow chart of what is going on:

What exactly is going on? The vi Host-ItchParser-TestHarness.vi, reads the file containing raw NASDAQ ITCH Market Data messages, sends them in to the FPGA Test Harness via the Host-to-Target DMA FIFO “HT-TEST_IN”. The Fpga test harness is located in the “Tests” folder and is named “Fpga-ItchParser-TestHarness.vi”, this Test Harness passes the raw Itch data as is to the Fpga-ItchParser.vi, which parses, normalized and filters each message for Add order message types only for symbol AAPL. It then sends an OrderBook command for each appropriate message back out to the Fpga-TestHarness which sends the results up to the host

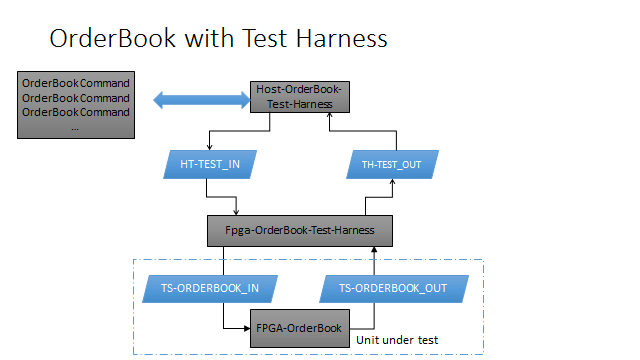

And for the OrderBook Test Harness

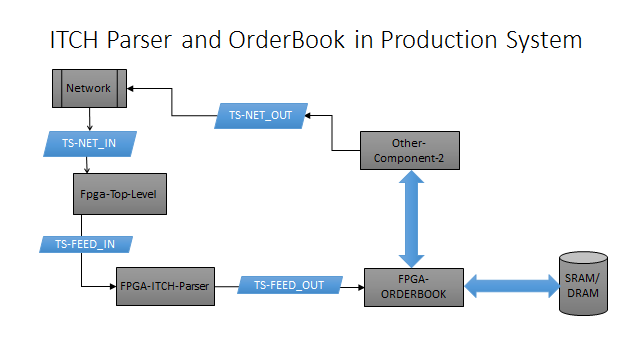

Here is what it would look like in a production system

Why this is so important?

Well, normally to create an FPGA based anything, one needs to use Verilog, VHDL or one of any numerous “high-level” design languages. Here you can accomplish the same thing, but with a really great programming interface that matches the Verilog programming model, but only with a graphical interface.

This means you can create a custom FPGA based solution, reduce your datacenter power usage, increase your applications performance, and reap the rest of the great benefits of FPGA-based computing.

I encourage you to download the source code for this and to see for yourself what LabVIEW for FPGA can do for you and to then try it in one of your own applications.

Stay Tuned… What is next?

- Hook the ITCH Parser up to an actual Network Interface Card, preferably a 10 Gigabit, since I already own the hardware to do so.

- Hook up either a MicroBlaze processor or the host computer to the OrderBook so that something can be done with the OrderBook data itself.

References:

- http://www.nasdaqtrader.com/content/technicalsupport/specifications/dataproducts/nqtv-itch-v4_1.pdf)