I wired up the 10 gigabit ethernet MAC to my MicroBlaze instance to my host computer and compiled/synthesized everything. I then turn on my “quiet” PXIe-1062Q and fire up my tester application and it did not work… I open up an isolated tester – “Fpga-Mac-Top.vi”, and it worked. I open up the isolated MicroBlaze tester – “Fpga-MicroBlaze-Top.vi”, and nothing. Not even a read from the GPIO.

This is quite strange… why is it not working? I spend some time looking over everything, re-generating output products, synthesizing from Vivado, bringing the design back in to LabVIEW, and long story short I was not setting the MicroBlaze Reset to ACTIVE_LOW, whereas in all of my previous designs I was setting it to ACTIVE_HIGH. Anyway, while I wait for it to compile, I have something to say. Which do you prefer? Using an IP Integration Node or a CLIP (Component Level IP) for using a MicroBlaze Processor from LabVIEW?

Well, first off, let me link to some National Instruments documentation on both:

- Importing External IP into LabVIEW FPGA:

- Using VHDL Code as Component-Level IP

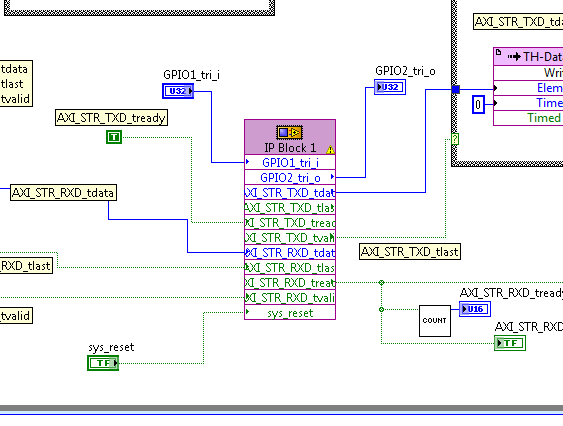

And now let me show you some screen shots. Here is a close up of what using an IP Integration Node looks like: (right-click to open in a new window for a larger version until I figure out how to modify this wordpress theme to be wider)

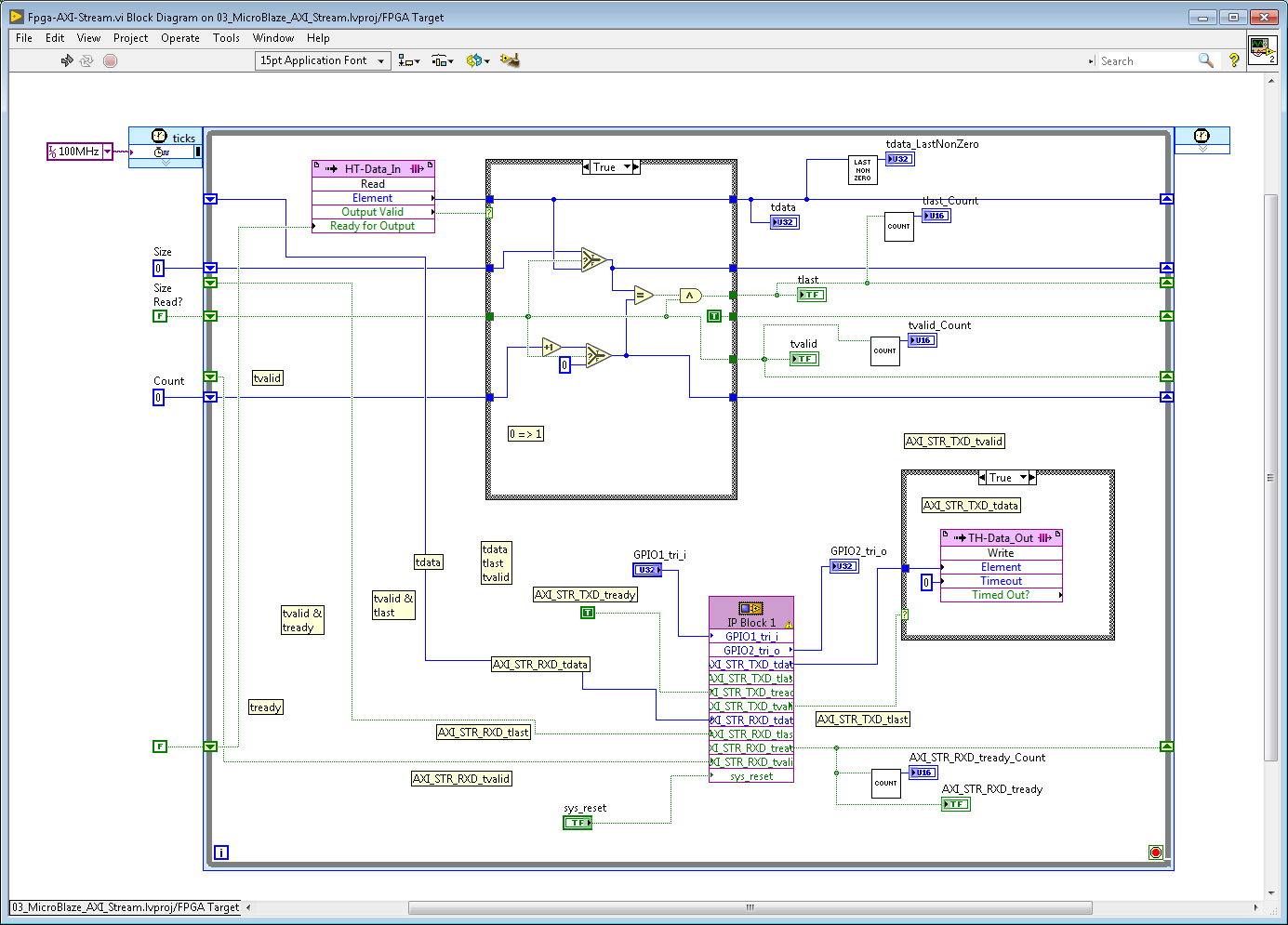

Here is a zoomed out version of this same VI:

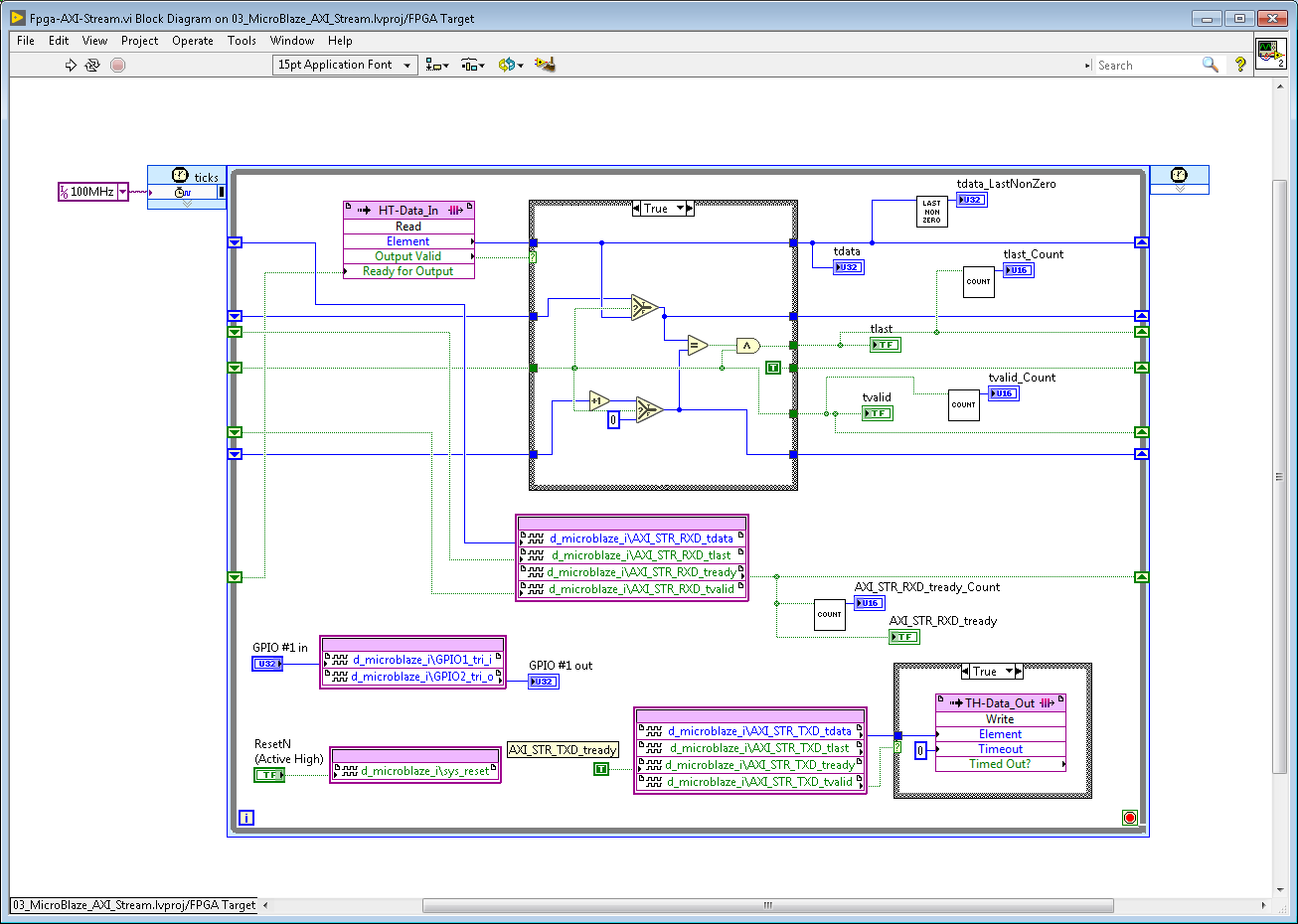

And finally, what it looks like without an IP Integration node, but with a CLIP (Component Level-IP):

Can you see the difference? I can… for starters, I can read the full name of each signal when using a CLIP. Additionally, with a CLIP I can split up my nodes in to separate locations, so that I can organize my VI in a much cleaner way. And finally, since I can read the full signal name when using a CLIP node, I no longer have to hover over each signal to get the signal name, thus removing any reason for having comments as in the IP Integration Node version.

Anyway. CLIP node is my recommended method of using LabVIEW FPGA to import Xilinx Vivado IP.

Also, this code was from a project that I implemented in order to learn how to use the AXI Stream FIFO inside of LabVIEW via a MicroBlaze. In other words, how to communicate with a MicroBlaze processor via an AXI Stream FIFO from LabVIEW FPGA.

See the source code here:

https://github.com/JohnStratoudakis/LabVIEW_Fpga/tree/master/06_MicroBlaze/03_MicroBlaze_AXI_Stream