So here is the most simple, FPGA-based Network Interface Card that I know of.

This application will start Port 0 of the 10 Gigabit Network interface that is provided by the PXIe-6592R (http://www.ni.com/en-us/support/model.pxie-6592.html) board by National Instruments, and will allow you to do any of the following:

- Check if any new ethernet frames have been received, and display the information, including the raw bytes of any such received frame

- Send a raw ethernet frame out of Port 0

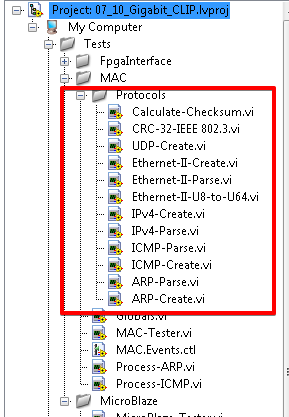

I have included the necessary code to parse and generate the following types of packets, enabling you to communicate with another computer on your network that supports:

- Ethernet II

- ARP

- ICMP

- IPv4

- UDP

The VI’s to do this are located in the directory “Tests/MAC/Protocols”, simply wire the incoming frame data to the “Parse” VI’s, or write the parameters in to the “Create” VI’s.

How to Parse Incoming Ethernet Frames

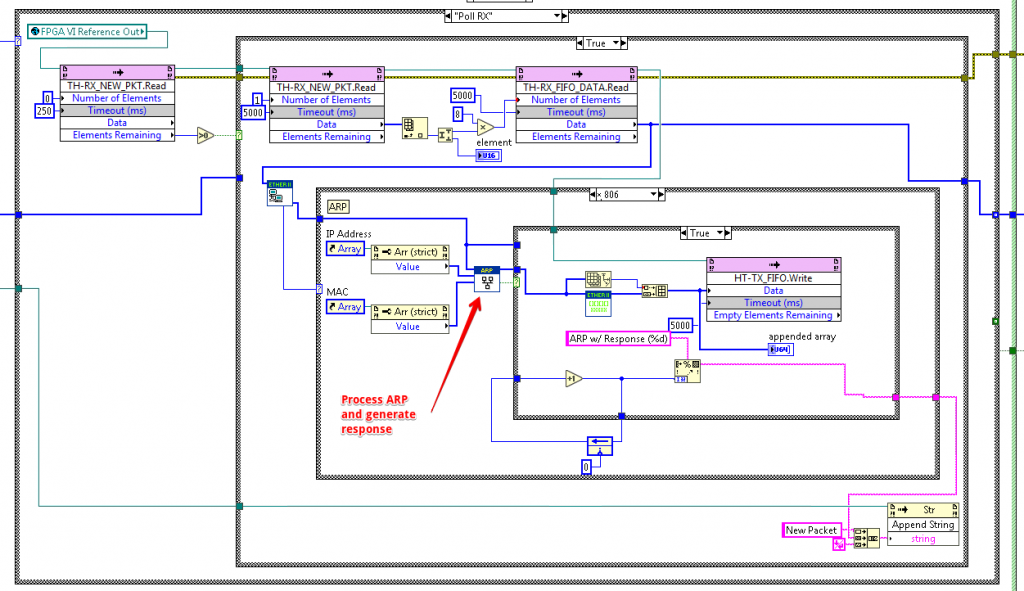

For an example of how to parse an incoming frame see the “Poll RX” case inside the bottom While Loop of the “MAC-Tester” vi:

How to Create Ethernet Frames

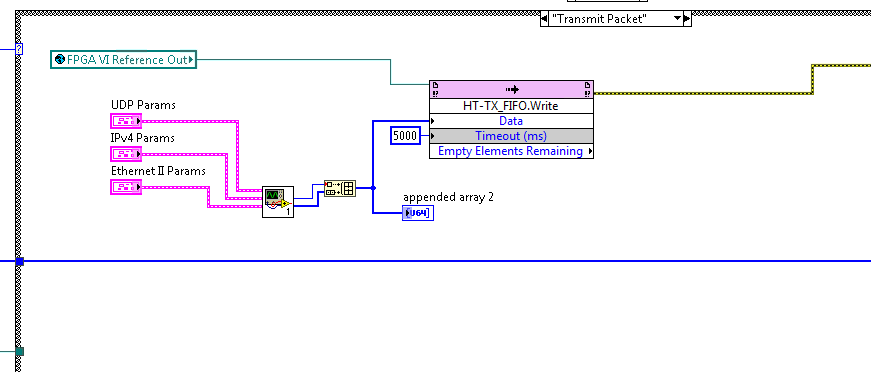

For an example of how to create a valid outgoing ethernet frame with a valid CRC32 on the end, see the “Transmit Packet” case inside the bottom While Loop of the “MAC-Tester” vi:

This vi calls the “UDP-Create.vi” and wires the size – in bytes – and the frame data in 64-bit words to the transmit FIFO.

Full Source Code

See the source code on GitHub here:

https://github.com/JohnStratoudakis/LabVIEW_Fpga/tree/master/07_10_Gigabit_CLIP

See the README.md for more documentation.

Next?

Now I have to take this code and wire it up to my MicroBlaze implementation that also sits inside the FPGA project. Only problem right now is that I have only figured out how to configure a 32-bit FIFO, and not a 64-bit FIFO. So I can either do some sort of translation inside the FPGA or hope and get lucky by configuring the FIFO to be 64 bits wide. Note: by FIFO, I am referring to an AXI-Stream FIFO.