I got something working – with live hardware plugged in to my network. I used the larger version of the Arty Artix-7 board, which cost $250 USD, and made my own custom reader for the LabVIEW FPGA Network library. I did not implement network writing features, nor do anything with the payload. Nevertheless, this is a Proof-of-Concept and can be used to make a nice FPGA accelerated network application.

Anyway, follow these instructions if you are Savvy enough with LabVIEW and you can examine the code.

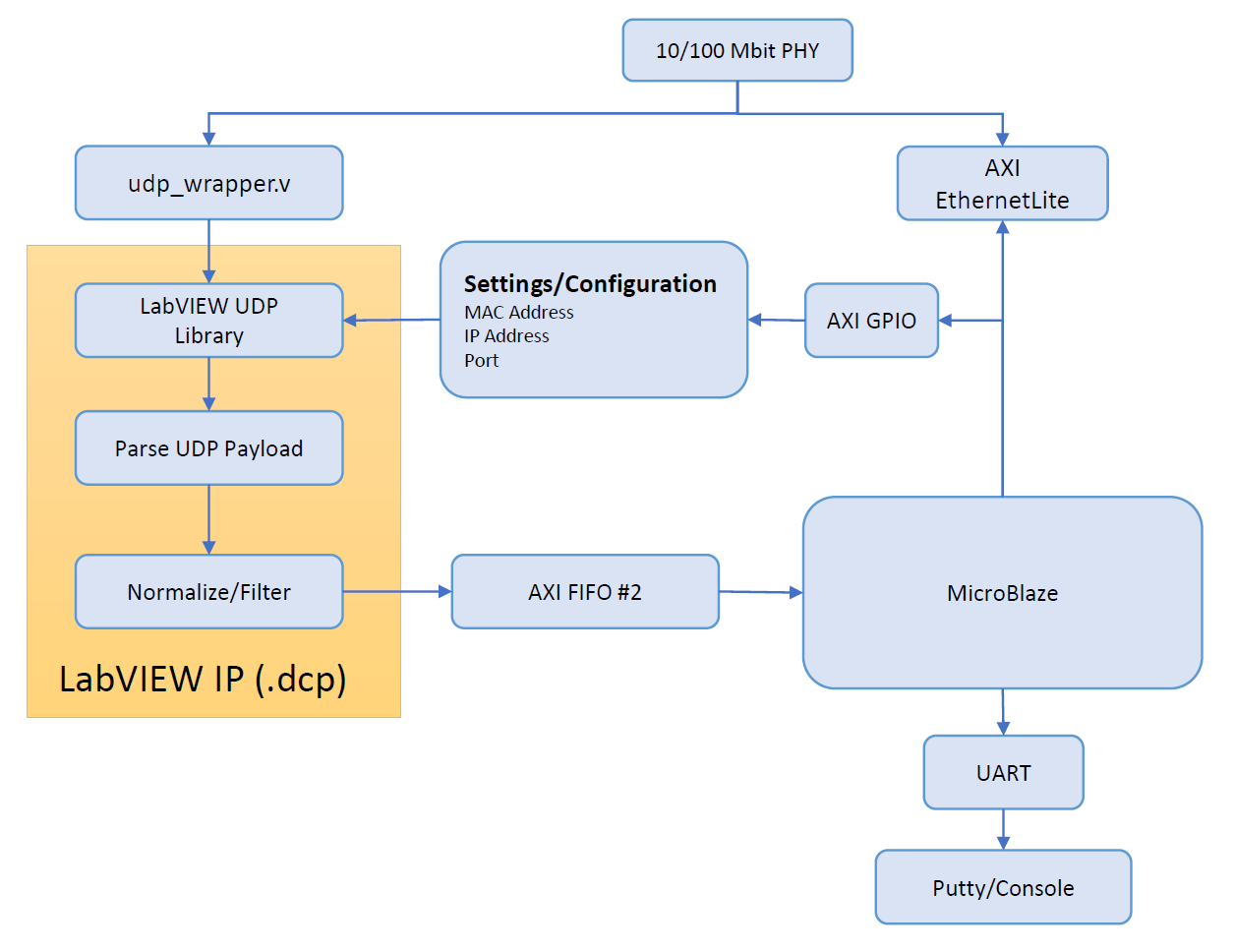

But first, a crude diagram of what is going on:

Hardware used:

- Arty A7: Artix-7 FPGA Development Board for Makers and Hobbyists

- Artix A7-100T Edition

- $250 USD

- https://store.digilentinc.com/arty-a7-artix-7-fpga-development-board-for-makers-and-hobbyists/

Source Repository:

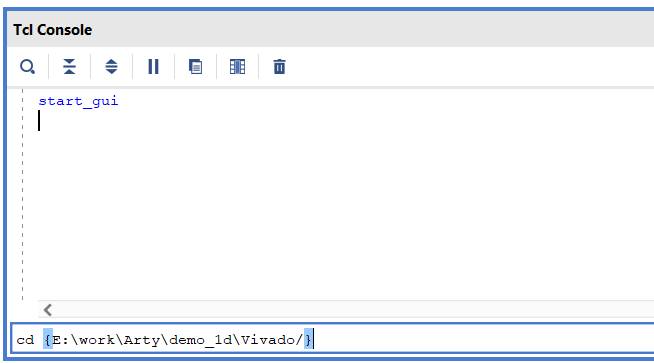

[1] – Load Vivado and change working to directory to where you cloned the repository – sub directory of vivado

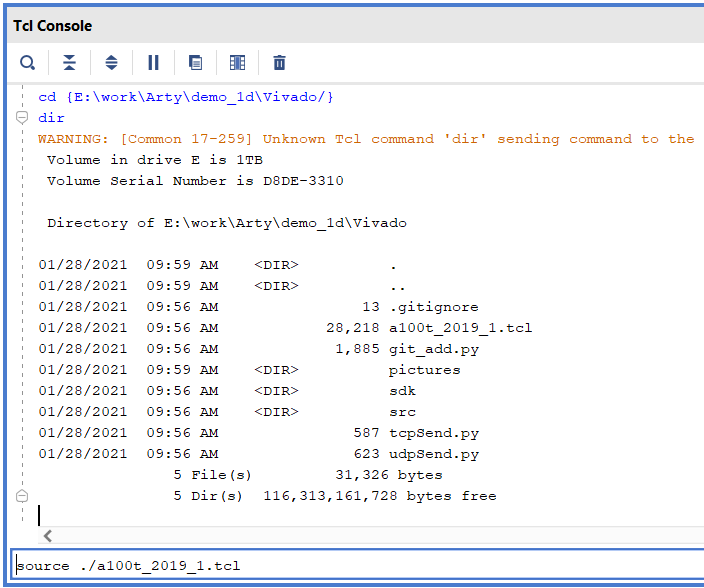

[2] Verify things are okay.

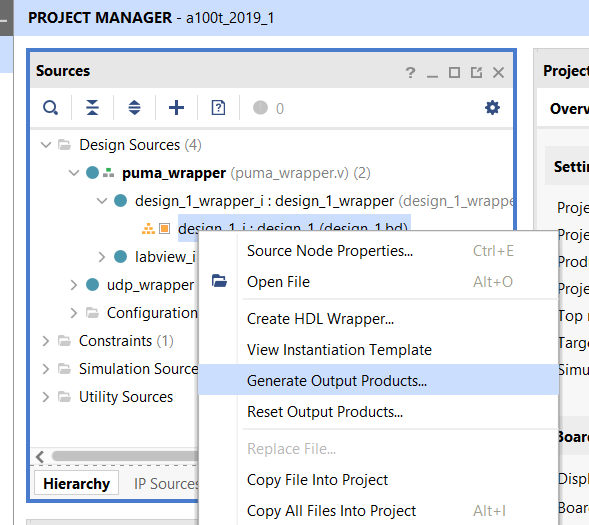

[3] Generate Output Products

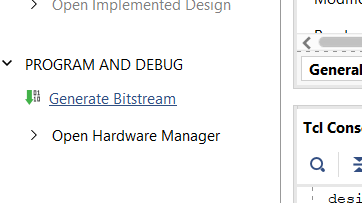

[4] Generate Bitstream

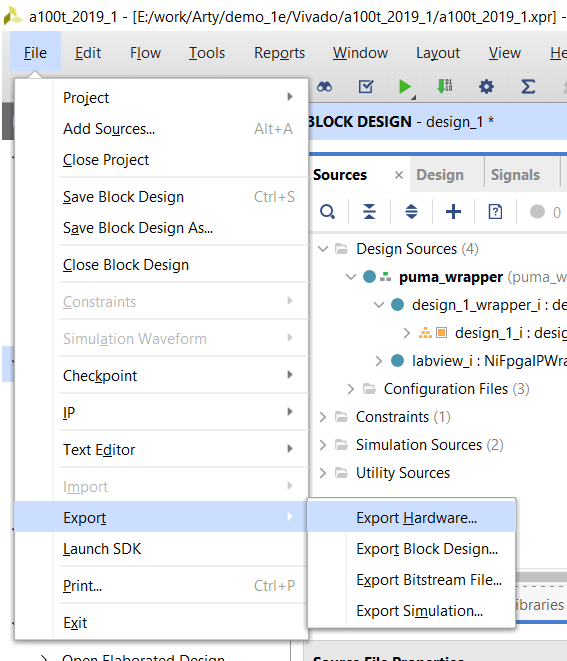

[5] Export Hardware

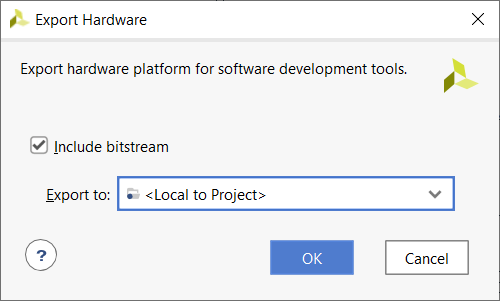

[6] Include Bitstream

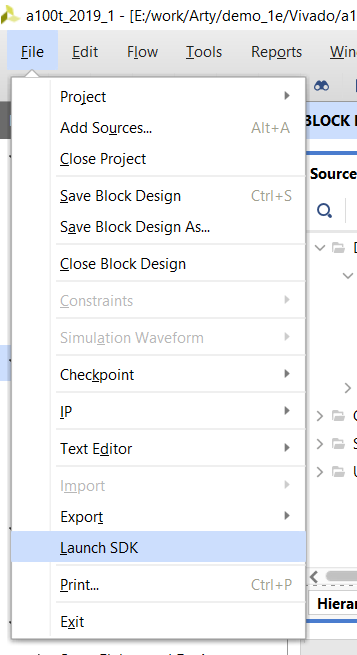

[7] Launch SDK

[8] Default Location

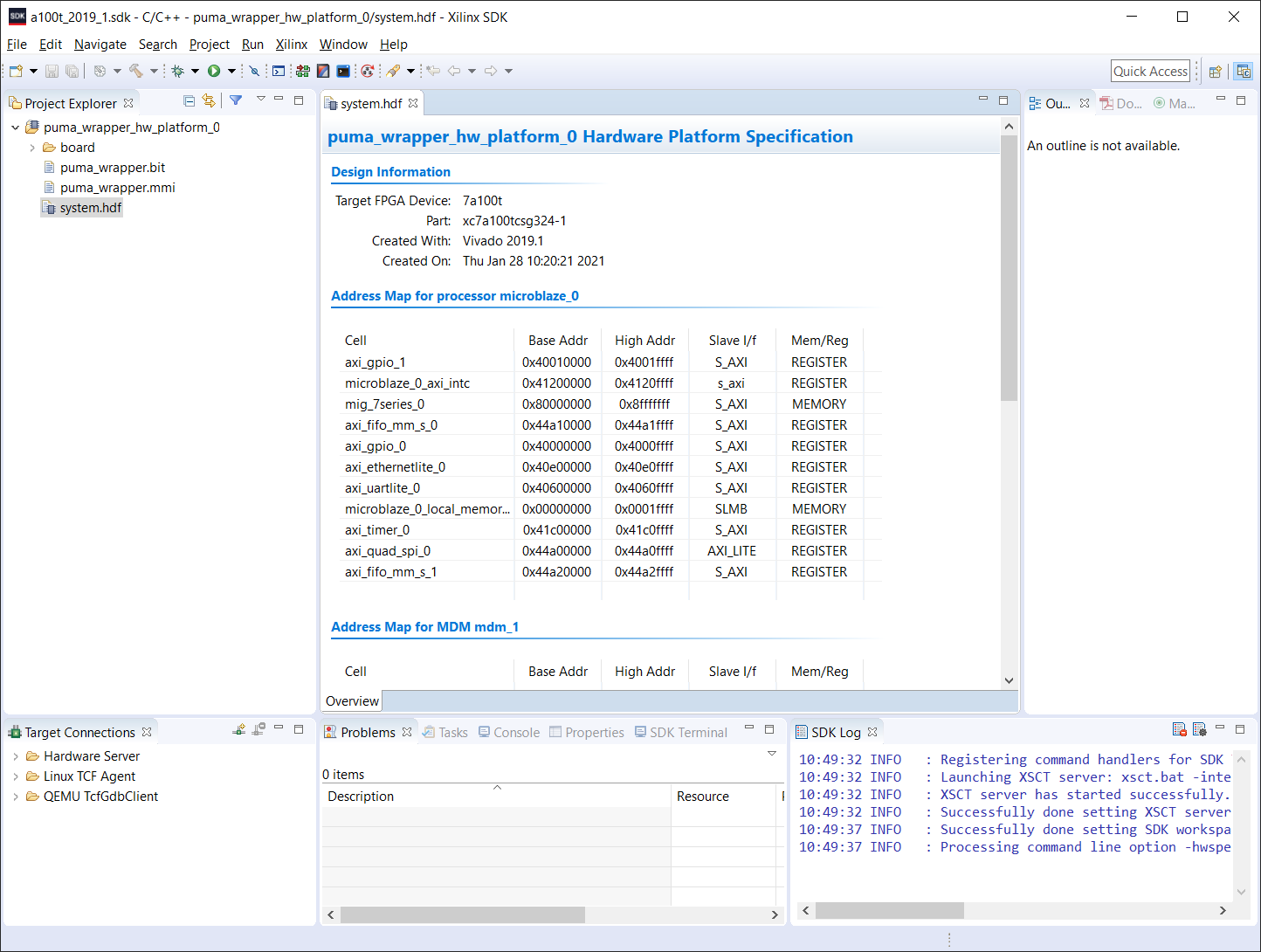

[9] SDK

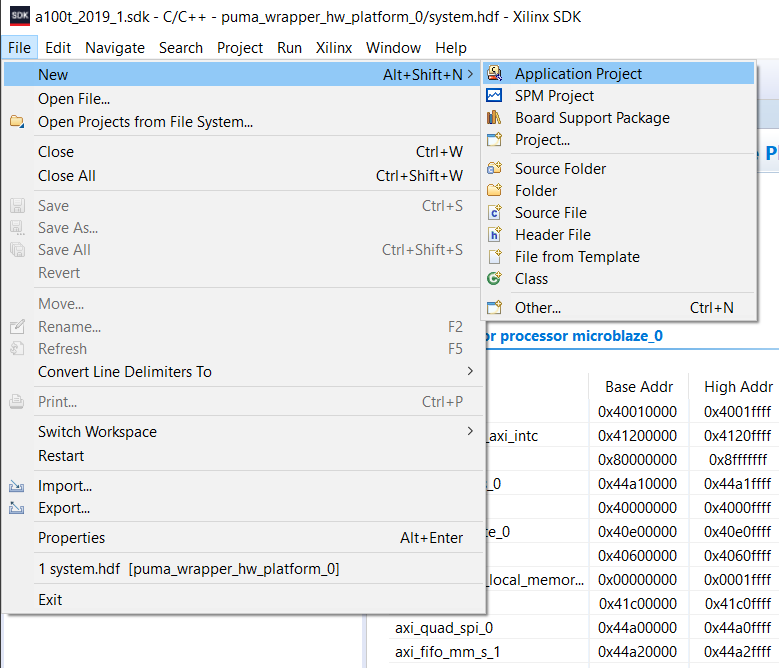

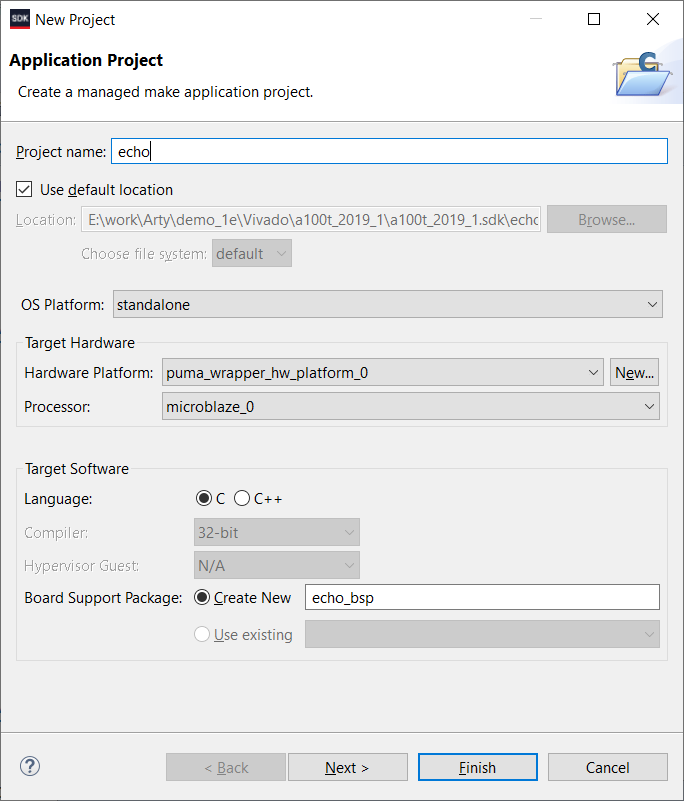

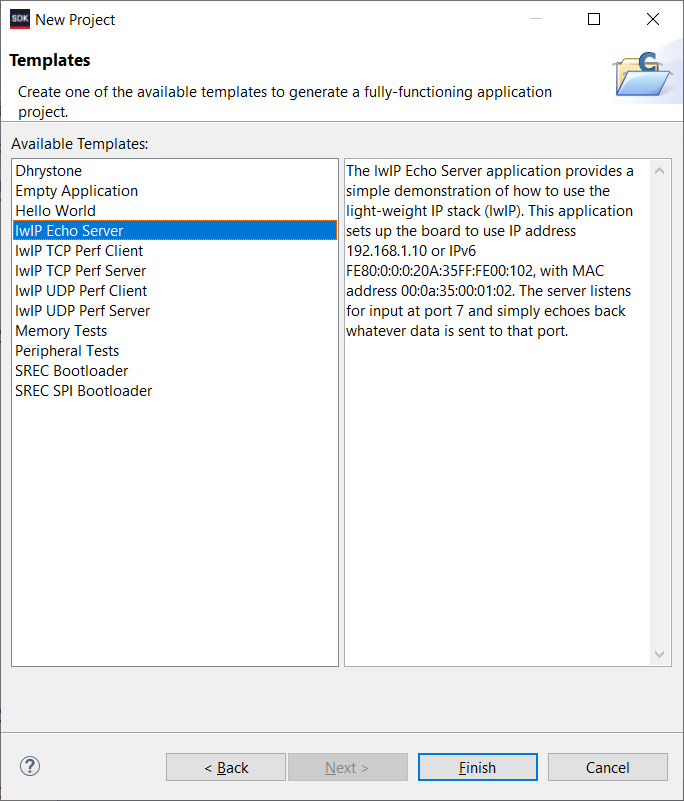

[10] Create Echo Application

[11] Select Next, not Finish

[12] Select lwIP Echo Application

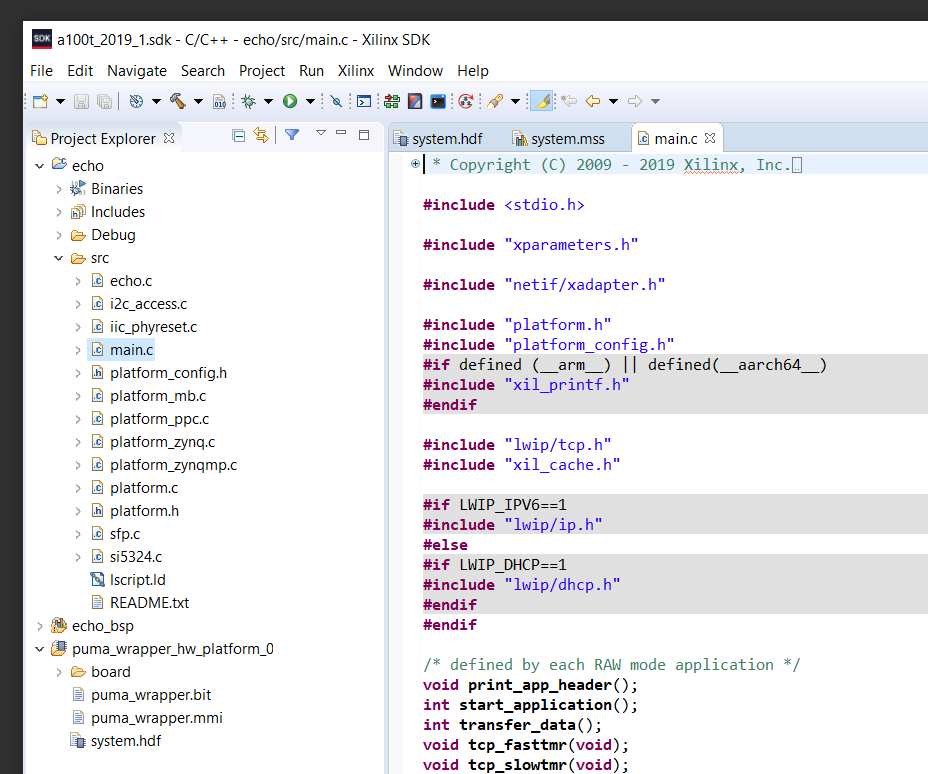

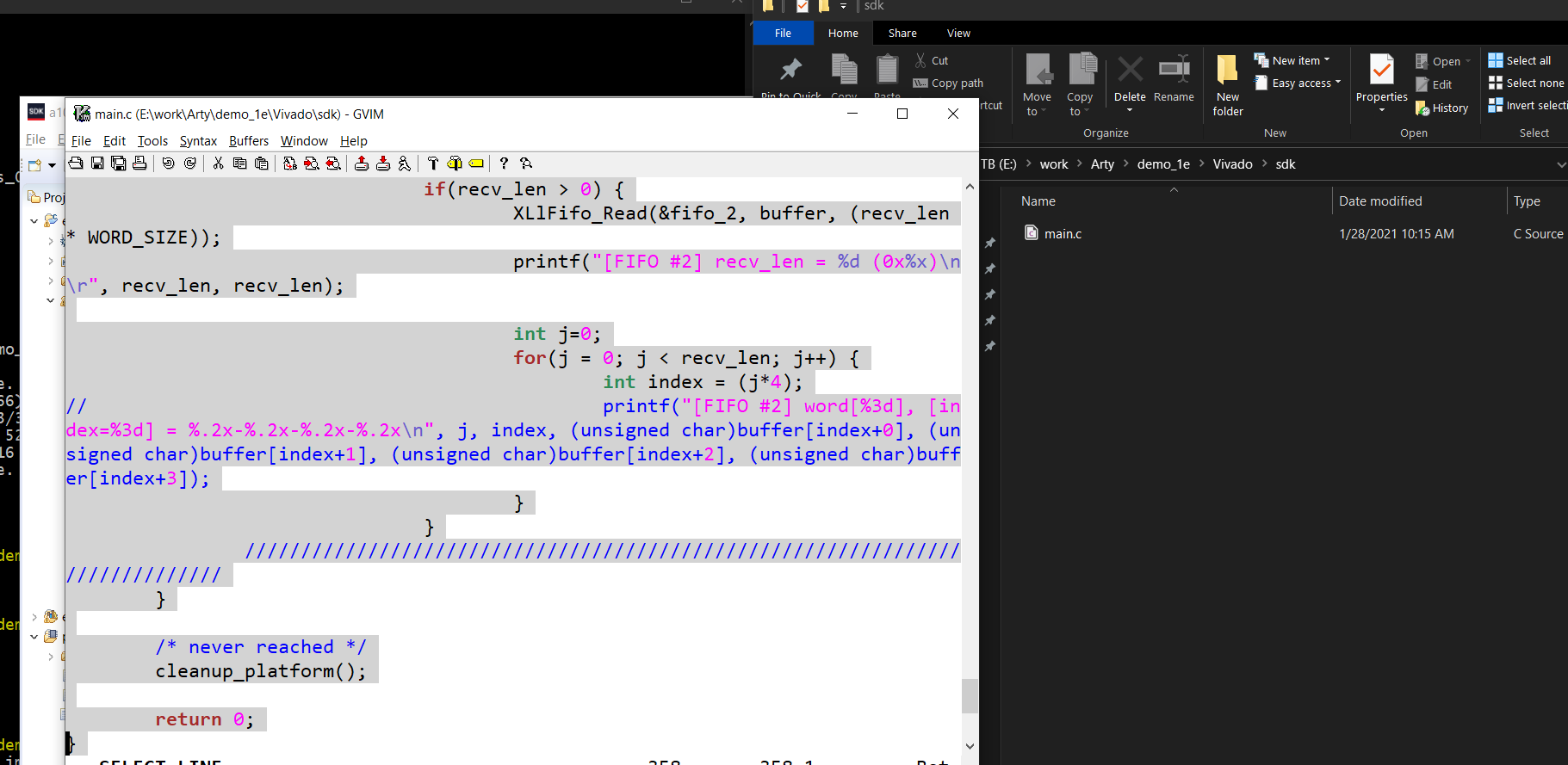

[13] Replace default main.c

[14] Overwriting it should just work

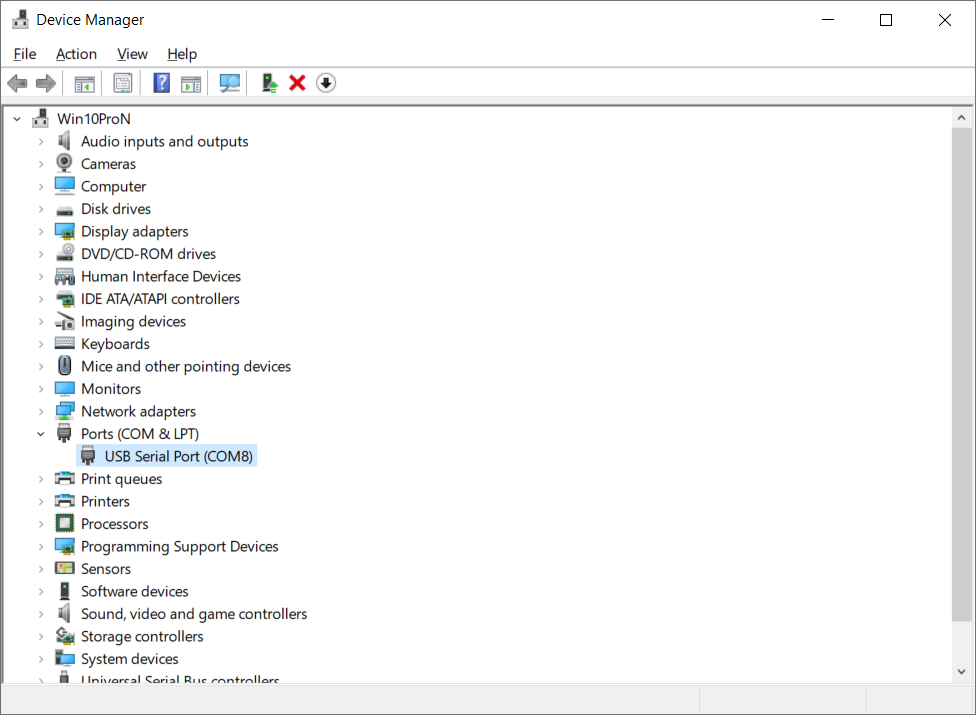

[15] Find COM Port

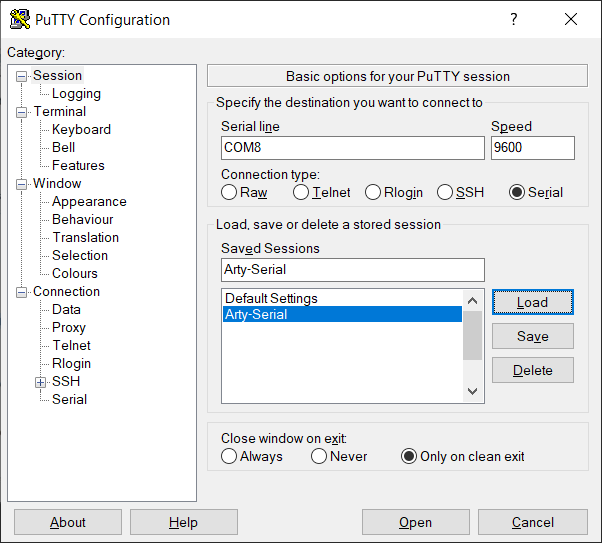

[16] Use Putty to connect

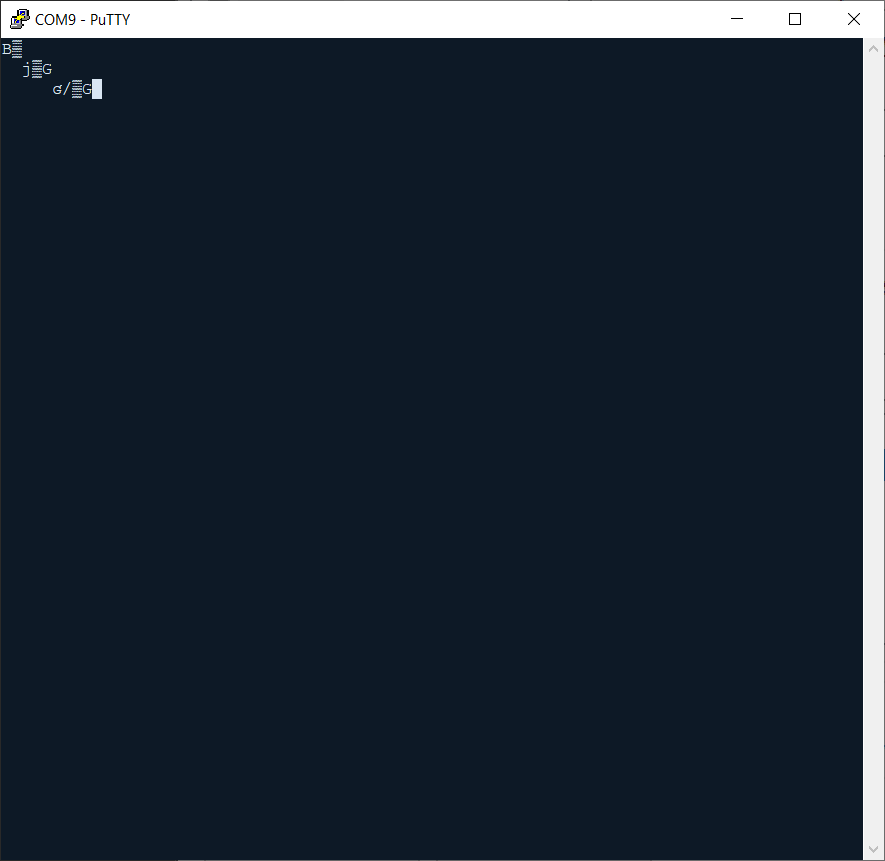

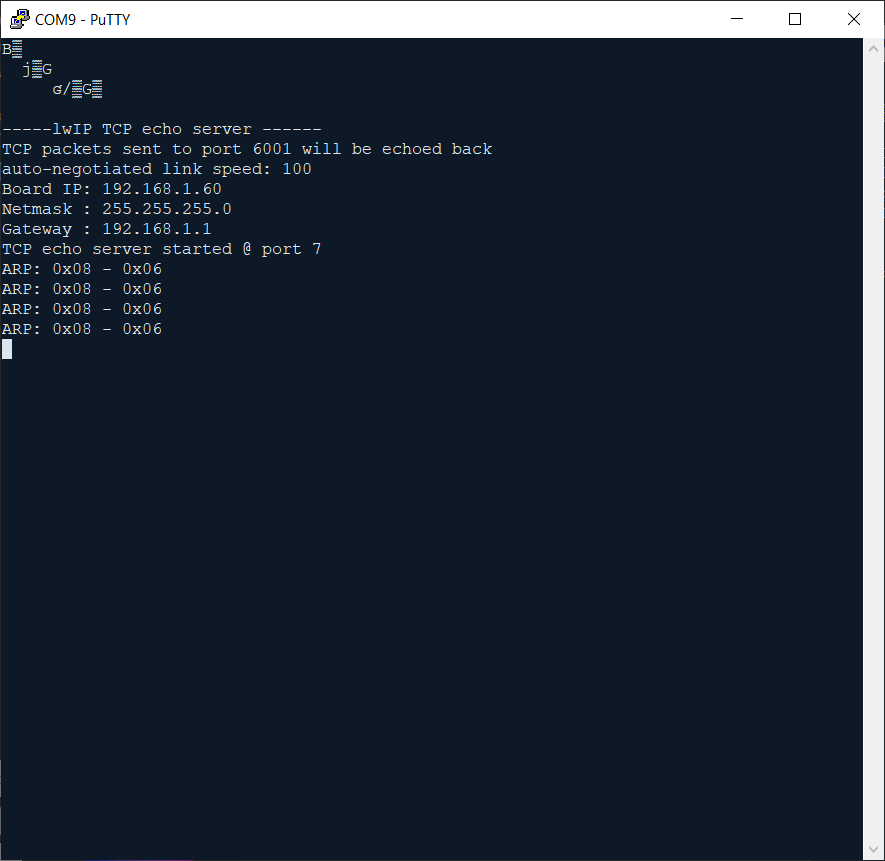

[17] Putty may not show clean output when you first connect

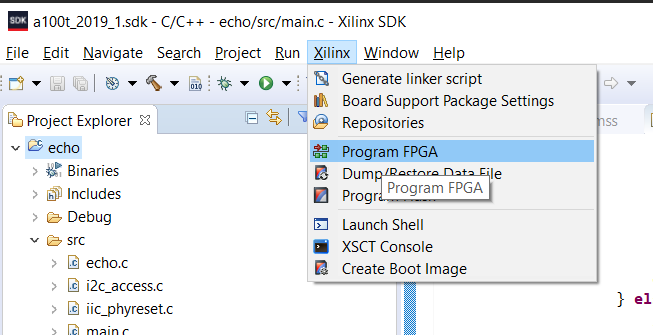

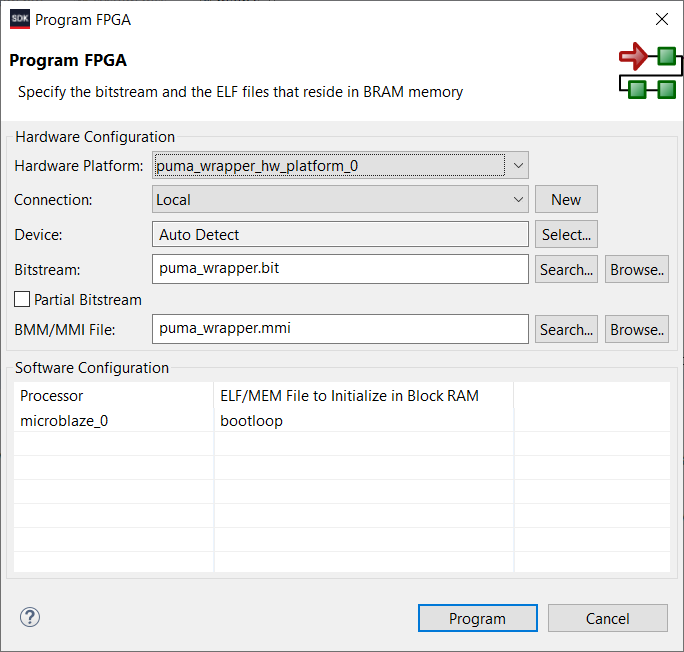

[18] First run Program FPGA

[19] Use defaults

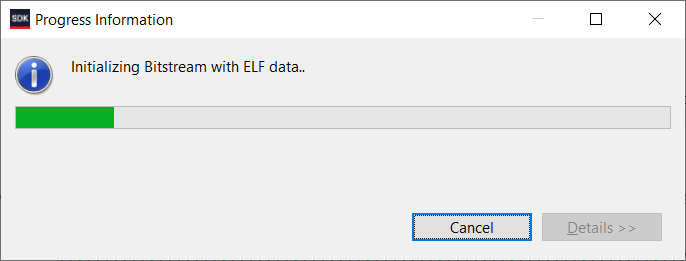

[20] Program FPGA progress

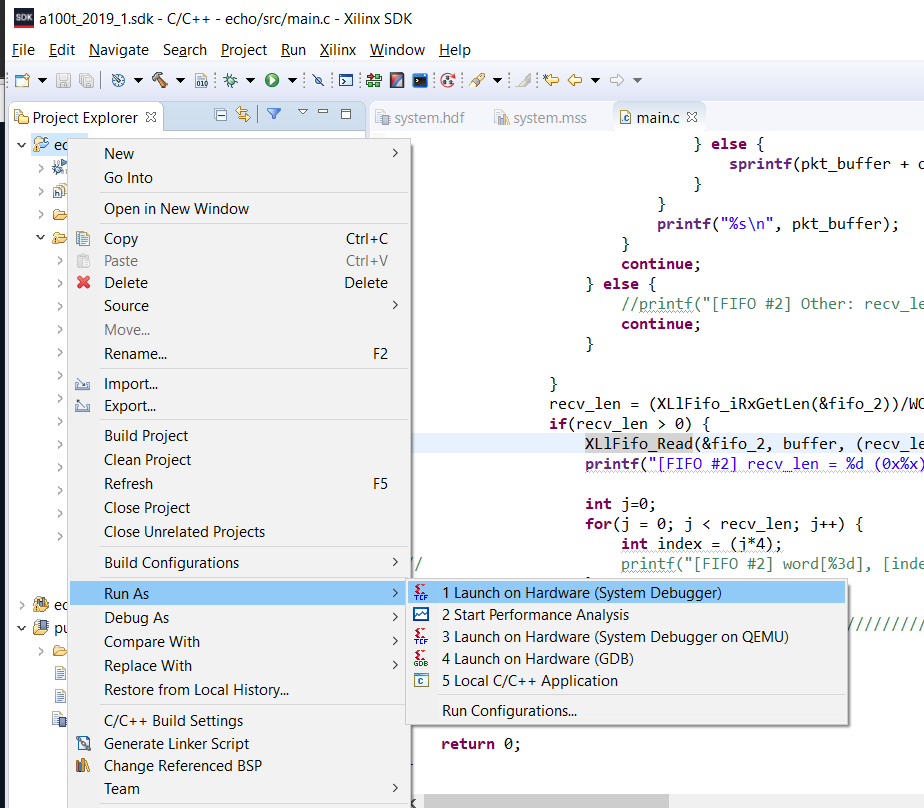

[21] SDK Start via Run As

[22] Putty output continues