What I have working right now:

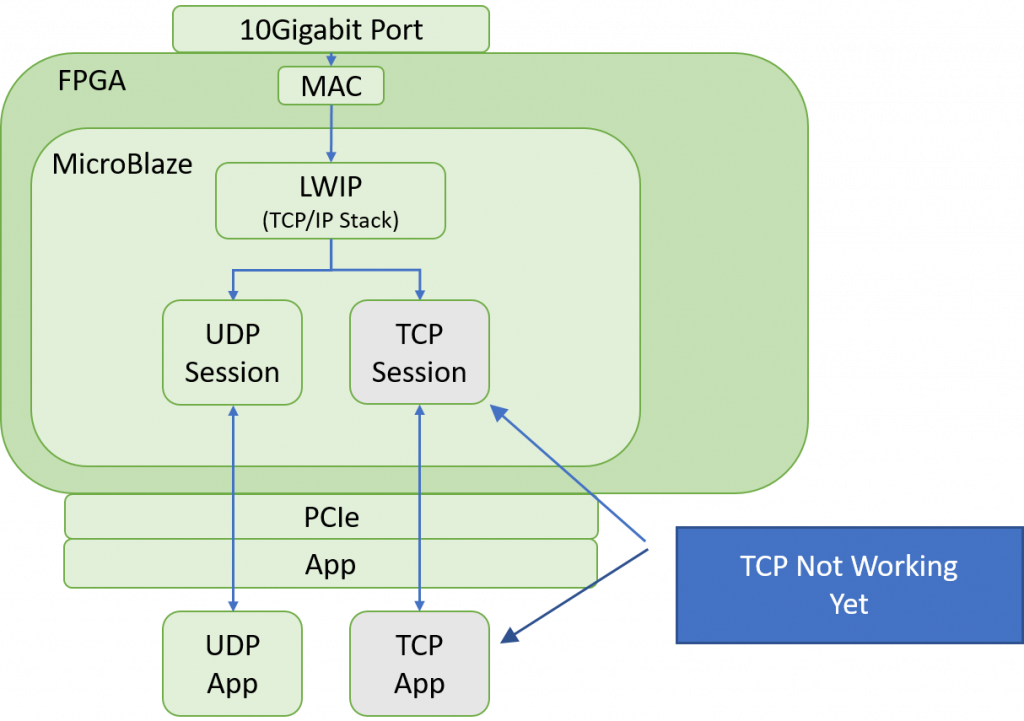

- A UDP packet enters the FPGA via the 10 Gigabit PHY that is connected to the FPGA.

- The 10 Gigabit Ethernet MAC running on the FPGA consumes the Ethernet Frame and passes it in to a c++ application running inside the MicroBlaze Processor.

- The MicroBlaze Processor is running a version of the open-source TCP/IP stack “lwip” which processes the UDP datagram, extracts the pertinent information and passes this information to a specific callback function that is implemented by the user. In this case that would be me.

- My implementation of this callback function sends a session identifier along with the payload out to the FPGA via an AXI FIFO.

- The FPGA implementation then takes this packet and forwards it to the host by using a LabVIEW Target-to-Host DMA FIFO.

Okay. So the end goal is to not send the UDP payload up to the host, but to send the UDP payload to another loop inside the FPGA. This loop will do some sort of analysis or “trading” with it. Additionally, instead of using UDP, I am currently working on the TCP version, I am just trying to figure out the lwip “RAW” TCP interface.

All code has been merged to the master branch, see github:

https://github.com/fpganow/MicroBlaze_lwIP

Here is a Crude Diagram

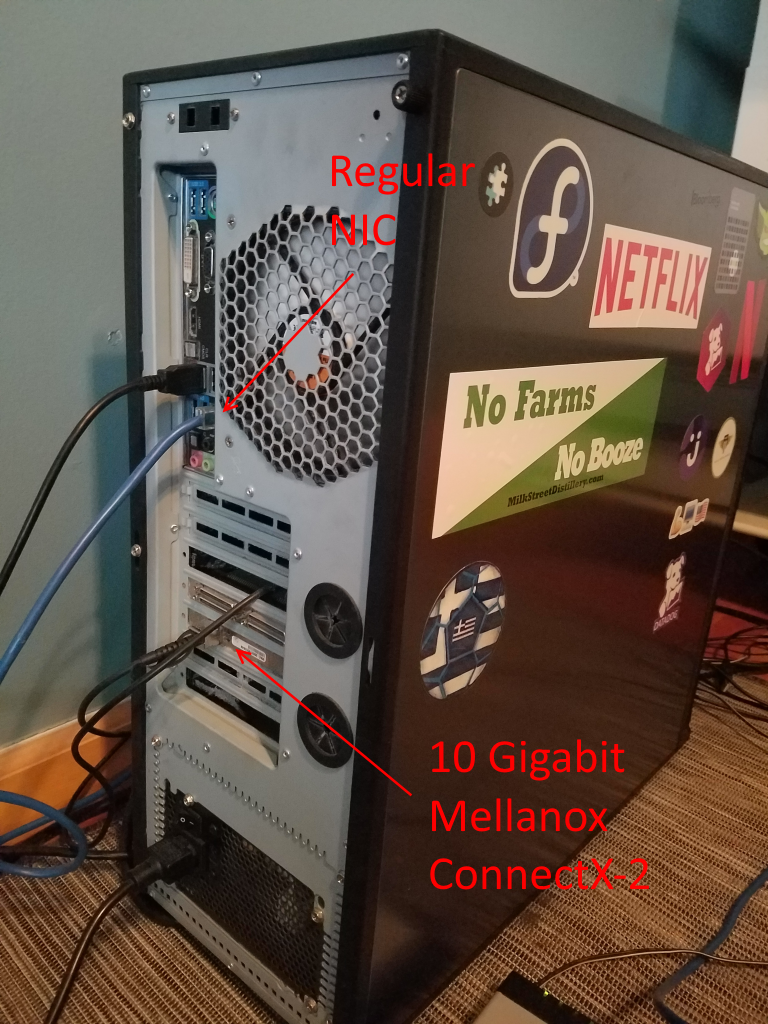

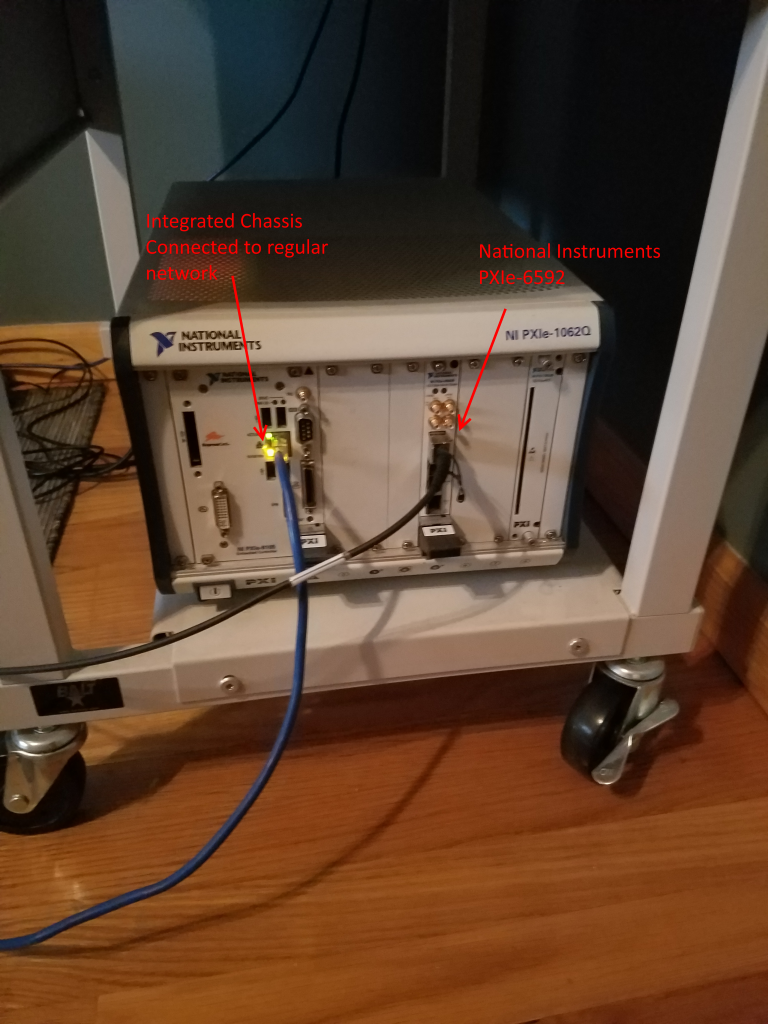

Here are a few pictures of my actual set up:

What’s Next?

- Implement TCP server

- Create a nice PowerPoint describing the architecture

- Consume UDP and TCP data on the FPGA, and do something that is ‘low latency’