So my workflow is as follows:

- Create IP in NI LabVIEW FPGA

- Export via FPGA IP Export Tool

- Creates a VHDL wrapper (.vhd)

- Places IP in Design Checkpoint (.dcp) file

- Open my Vivado Block Design

- Use or update the VHDL wrapper that uses the Design Checkpoint

- Synthesis, Implementation, and Run

The NI LabVIEW FPGA IP Export utility provides you with 2 files, a design checkpoint and a wrapper file to use for instantiating your IP using VHDL.

A wrapper file is a very simple vhdl file, it contains the following interface to your design:

| entity NiFpgaIPWrapper_fpga_top is port ( reset : in std_logic; enable_in : in std_logic; enable_out : out std_logic; enable_clr : in std_logic; ctrlind_00_d : in std_logic_vector(0 downto 0); ctrlind_01_d_latched : out std_logic_vector(0 downto 0); ctrlind_02_c : in std_logic_vector(0 downto 0); ctrlind_03_c_echo : out std_logic_vector(0 downto 0); ctrlind_04_b : in std_logic_vector(0 downto 0); ctrlind_05_a : in std_logic_vector(0 downto 0); ctrlind_06_a_and_b : out std_logic_vector(0 downto 0); ctrlind_07_a_or_b : out std_logic_vector(0 downto 0); Clk40 : in std_logic ); end NiFpgaIPWrapper_fpga_top; |

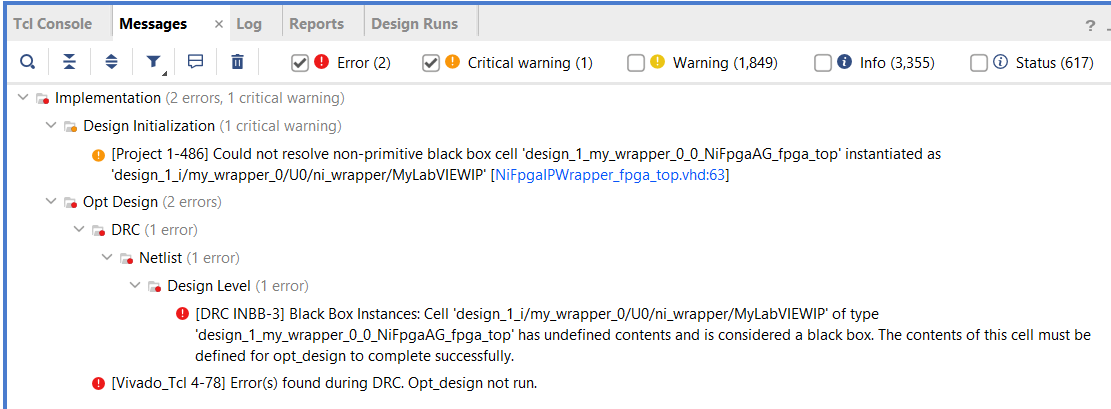

However, in some situations using this method results in a problem, specifically Vivado will give a ‘Black Box Undefined error’ during the opt_design step of the Implementation phase.

| “ERROR: [DRC INBB-3] ‘Black Box Instances: Cell ‘design_1_i/…’ of type ‘design_1_i/…’ has undefined contents and is considered a black box. The contents of this cell must be defined for opt_design to complete successfully.” |

I have created a github.com repository where I have isolated this problem and make it very easy for someone to reproduce this error:

https://github.com/fpganow/black.box

But first, here is a screenshot of the error message: (left-clicking always opens in a new tab)

Log output:

https://github.com/fpganow/black.box/blob/main/pictures/black.box.instance.error.txt

|

|

And then I removed the .dcp file from my vivado project and used the generated .v file.

Also, I chose to use -rename_top just to be sure that the IP I was exporting has the name I am expecting.